이번 포스팅부터는 유명한 테스트 아이템 항목들을 다뤄보고자 합니다.

첫번째로 Under Voltage Lock Out이라 해서 UVLO라고 짧게 부릅니다.

얘 쉽게 말하자면 문턱전압 재는거에요. 근데 왜이렇게 어려운 말을 쓰느냐?

문턱전압에 영향을 주는게 2가지가 있기 때문입니다. 바로 Input전압과 Power전압입니다.

일반적으로 우리가 아는 문턱전압은 예를 들면, Input전압을 0V에서 15V까지 천천히 증가시키면서 Output이 어떤 Input 전압 값에서부터 발생하는지 확인하는 것이었습니다.

UVLO는 Power전압을 0V to 15V로 증가시키면서 Output이 어떤 Power 전압 값에서부터 발생하는지 확인하는 것입니다. 아래 표로 깔끔히 정리해놨습니다.

| UVLO | V_th | |

| 공통점 | 두 항목 모두 Output 파형이 언제부터 발생하는지 알아보기 위함 | |

| 차이점 | Power전압에 변화를 주고, Input전압은 고정시킴. (이 때, Input은 펄스파) | Input전압에 변화를 주고, Power전압을 고정시킴. (Power는 펄스파 X. 그냥 DC) |

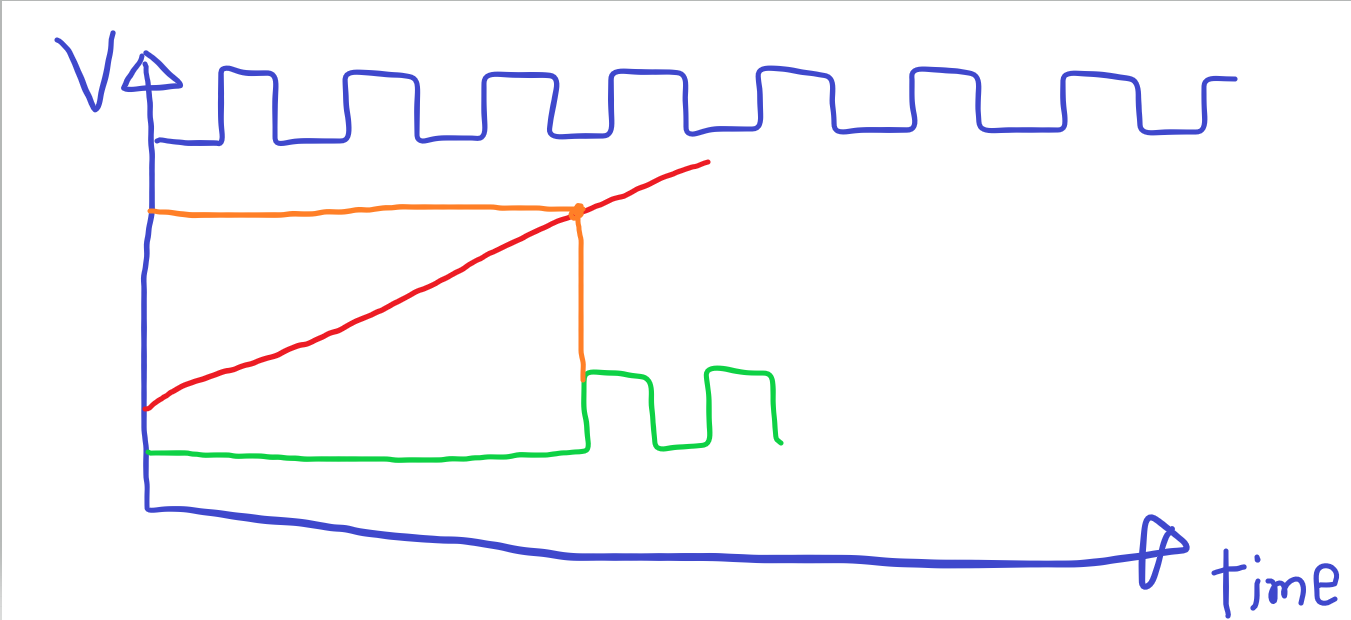

1. 파란색 펄스파 : Input 전압

2. 빨간색 선 : Power 전압

3. 초록색 펄스파 : Output 전압

x축 전압 / y축 시간

1,2,3번 전압에서 아웃풋이 인풋 값보다 낮다 그런 의미는 아닙니다. 그냥 하나의 그래프에 모든걸 담으려고 한거구요.

Input,Output전압은 0V to 5V 펄스파라 생각하시고 빨간색 Power전압은 0V에서 15V로 증가시키고 있다 생각하시면 되겠습니다.

자, 일단 여기까지 잘 따라오셨나요? 추가로 하나만 더 설명하고자 합니다. 지금 제가 그린 그래프를 보면 Output이 발생하는 시점을 다루고 있어요. 그럼 반대로 Output이 꺼지는 시점도 중요하지 않을까요? 당연하게도 테스트 아이템에 필수적으로 포함되는 항목 중 하나입니다.

Hysteresis

- 히스테리시스라 부릅니다. UVLO 그리고 V_th에 항상 포함되는 테스트 아이템입니다. 위에서 말한대로 Output이 발생하게 되는 시점을 UVLO+(V_th+) , Output이 꺼지는 시점을 UVLO- (V_th-)라고 합니다. 그리고 이 두 값의 차이를

Hysteresis라 부릅니다.

알록달록하다, 그죠? (랄로식 말투)

주황색 +가 UVLO+ , 노락색 -가 UVLO-입니다.

히스테리시스가 중요한 이유는 디바이스가 언제 동작을 하고, 꺼질지 알아야 하기 때문입니다. 만약 Hysteresis가 0에 가까우면 디바이스가 우리의 의도와 다르게 지멋대로 켜지거나 꺼질 수 있습니다. 따라서 어느정도의 Gap을 보장받아야 합니다. 이런 점때문에 중요한 항목 중 하나입니다.

'Test Engineer (전 직장)' 카테고리의 다른 글

| [Test] # 5. 테스트 리소스에 대하여 (0) | 2022.01.23 |

|---|---|

| [Test] # 4. 릴레이 (Relay) 소자의 동작원리 (1) | 2022.01.23 |

| [Test] # 3. Analog to Digital Converter & accuracy와 resolution에 대하여 (0) | 2022.01.23 |

| [Test] # 1. 테스트 양산 엔지니어 vs 테스트 개발 엔지니어 (17) | 2022.01.23 |

| [Test] # 0. 반도체 테스트 직무에 대한 설명 (테스트 엔지니어에게 요구되는 역량은?) (4) | 2022.01.23 |